TI SK-AM62

Jump to navigation

Jump to search

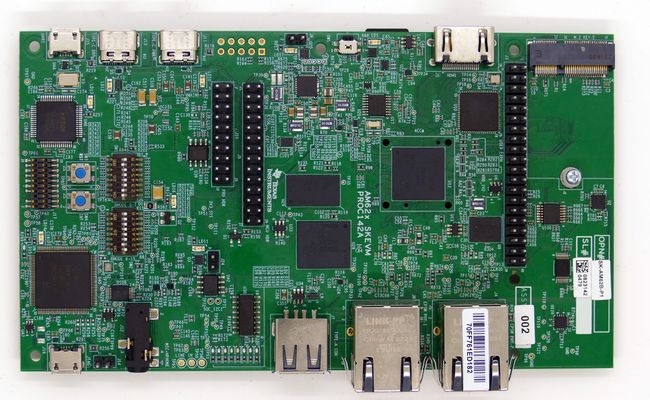

This article describes specifics for the TI SK-AM62 evaluation board.

Preparing for J-Link

- Write the following boot image to the SD card with no offset:File:TI SK-AM62 boot.bin

For example:

dd if=TI_SK-AM62_boot.bin of=/dev/sdc bs=512; sync

- Set the following boot configuration (SW1, SW2):

| Position | State |

|---|---|

| BIT0 | ON |

| BIT1 | ON |

| BIT2 | OFF |

| BIT3 | OFF |

| BIT4 | OFF |

| BIT5 | OFF |

| BIT6 | ON |

| BIT7 | ON |

| BIT8 | OFF |

| BIT9 | ON |

| BIT10 | OFF |

| BIT11 | OFF |

| BIT12 | ON |

| BIT13 | OFF |

| BIT14 | OFF |

| BIT15 | OFF |

- Connect the J-Link to JTAG connector (J17) using J-Link TI-20-CTI adapter (J-Link TI-20-CTI Adapter).

- Power the board via USB Type-C connector (J13).

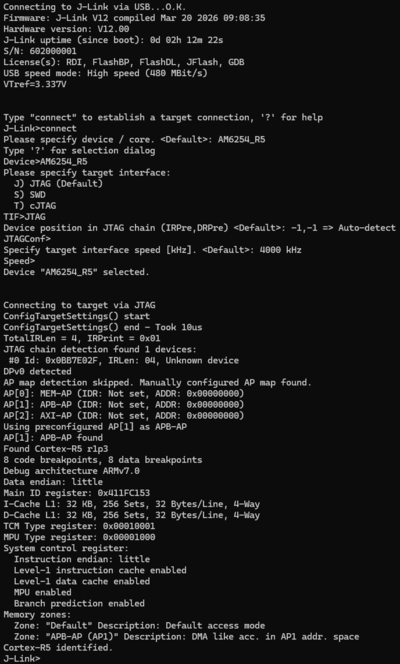

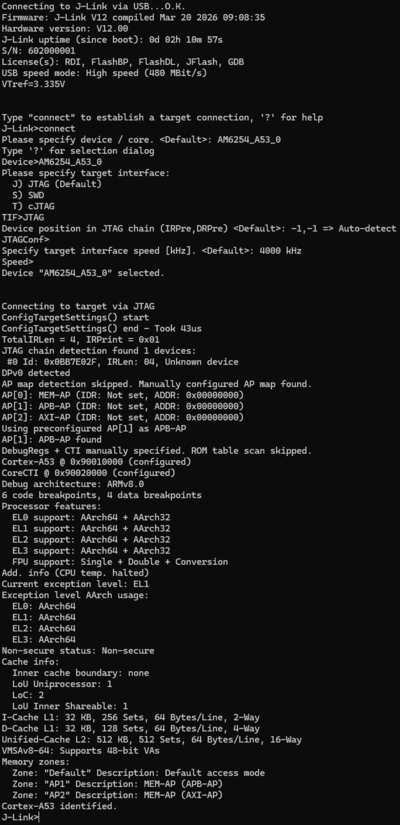

- Verify the Connection with e.g. J-Link Commander. The output should look as follows:

- Cortex-R5 connection:

- Cortex-A53 connection:

Example Project

The following example project was created with the SEGGER Embedded Studio project wizard and runs out-of-the-box on the NXP MCIMX93-EVK.

It is a simple Hello World sample linked into the internal flash.

Coretex-R5

SETUP

- Embedded Studio: V8.24

- Hardware: TI SK-AM62

- Link: File:TI SK-AM62 R5 TestProject ES V826b.zip

Coretex-A53

SETUP

- Embedded Studio: V8.24

- Hardware: TI SK-AM62

- Link: File:TI SK-AM62 A53 TestProject ES V826b.zip